Digitalt högtalarfilter i FPGA Ver 0.1,

IIR Filter

Just nu planerar jag inte att ändra mera på IIR filtret, därför får det en egen punkt i pressentationen.

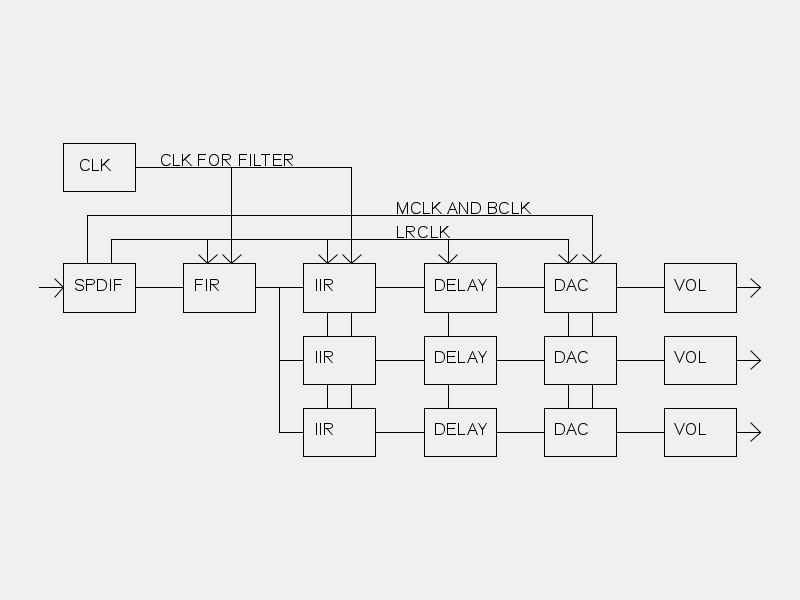

IIR filtret är tänkt att användas som delningsfilter. Systemet har tre stereo utgångar, som kan användas t.ex. för bas, mellan och diskanthögtalare.

Filtren är uppbygda i biquad moduler. Kanal ett och tre har två stycken, och kanal två har fyra st.

Varje biquad behöver 5st 35 bitars konstanter. För varje samplingsfrekvens behövs en egen uppsättning konstanter. Detta leder till att det totalt behövs: 6 st fs * 8 st biquad * 5 konstanter/biquad = 240 st 35 bitarskonstanter. Eftersom det hade varit lite omständigt att skriva om dessa för hand varje gång man vill ändra delningsfrekvens har jag skrivit ett scilabskript som skapar vhdl filen med konstanterna i.

I filen finns även presets för amplitud och tidsfördröjning till de olika utgångarna. Om man i stället vill att värdet som sätts i menyn ska sparas till nästa gång som filtret startas upp, kan delayerna sättas till 255 och amplituderna till + 10,5 dB. Då laddas värdena från eeprom kretsen i stället.

Scilabskript för att skapa konfigurationsfil i VHDL